# ADM-XRC-7Z1 User Manual

Document Revision: 2.6 14th February 2022

#### © 2022 Copyright Alpha Data Parallel Systems Ltd. All rights reserved.

This publication is protected by Copyright Law, with all rights reserved. No part of this publication may be reproduced, in any shape or form, without prior written consent from Alpha Data Parallel Systems Ltd.

Head Office

Fax:

email:

LIS Office

Address: Suite L4A, 160 Dundee Street, Edinburgh, EH11 1DQ, UK

Telephone: +44 131 558 2600 +44 131 558 2700 sales@alpha-data.com website: http://www.alpha-data.com 10822 West Toller Drive, Suite 250 Littleton, CO 80127 (303) 954 8768

(866) 820 9956 - toll free sales@alpha-data.com http://www.alpha-data.com

All trademarks are the property of their respective owners.

# Table Of Contents

| 1       | Overview                                 |    |

|---------|------------------------------------------|----|

| 11      | Introduction                             |    |

| 1.2     | Key Features                             |    |

| 1.3     | Order Code                               |    |

| 1.3     | References & Specifications              |    |

| 2       | PCB Information                          |    |

| 21      | Physical Specifications                  |    |

| 2.1     | Motherboard / Carrier Requirements       |    |

| 2.3     | Power Requirements                       |    |

| 3       | Installation                             |    |

| 31      | Software Installation                    |    |

| 3.1     | Sottware Installation                    |    |

| 3.2.1   | Handling Instructions                    |    |

| 3.2.1   | Installation in ADC-XMC-Breakout Carrier |    |

| A 3.2.2 |                                          |    |

| 41      | Functional Description                   |    |

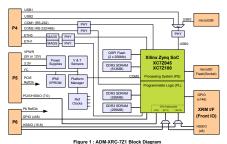

|         | Overview                                 |    |

| 4.1.1   | Switch Definitions                       |    |

|         | LED Definitions                          |    |

| 4.2     | Primary XMC Connector P5                 |    |

| 4.2.1   | XMC Platform Interface                   |    |

| 4.2.1.1 | IPMI I2C                                 |    |

| 4.2.1.2 | MBIST#                                   |    |

| 4.2.1.3 | MVMRO                                    |    |

| 4.2.1.4 | MRSTI#                                   |    |

| 4.2.1.5 | MRST0#                                   |    |

| 4.2.1.6 | MPRESENT#                                |    |

| 4.2.1.7 | JTAG                                     |    |

| 4.2.2   | P5 HSSIO Links                           |    |

| 4.3     | Secondary XMC Connector P6               |    |

| 4.3.1   | P6 HSSIO Links                           |    |

| 4.3.2   | P6 GPIO Signals                          |    |

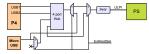

| 4.4     | PrPMC Connector P4                       |    |

| 4.5     | JTAG Interfaces                          |    |

| 4.5.1   | On-board Interface                       |    |

| 4.5.2   | XMC Interface                            |    |

| 4.5.3   | JTAG Voltages                            |    |

| 4.6     | Clocks                                   |    |

| 4.6.1   | PCIe Reference Clock (PCIEREFCLK)        |    |

| 4.6.2   | P6 Reference Clock (P6REFCLK)            |    |

| 4.6.3   | MGTCLK250M                               |    |

| 4.6.4   | PROGCLK                                  |    |

| 4.6.5   | REFCLK200M                               |    |

| 4.6.6   | PS_CLK33M3                               |    |

| 4.6.7   | USB_REFCLK24M                            |    |

| 4.6.8   | ETH_CLK25M                               |    |

| 4.6.9   | ETH1_CLK125M                             |    |

| 4.7     | Resets                                   |    |

| 4.8     | Zyng PS Block                            |    |

| 4.8.1   | Boot Modes                               |    |

| 4.8.2   | PS Memory Interfaces                     |    |

| 4.8.2.1 | Quad SPI Flash Memory                    |    |

| 4.8.2.2 | MicroSD Flash Memory                     | 13 |

| 4.8.2.3                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| 4.8.3                                                                                                                                                                                       | Ethernet Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                         |

| 4.8.4<br>4.8.5                                                                                                                                                                              | Serial COM Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                         |

| 4.8.5                                                                                                                                                                                       | USB Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                         |

| 4.91                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                         |

| 4.9.1                                                                                                                                                                                       | PL DDR3 Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                         |

| 4.9.2                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                         |

| 4.9.2.1                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                         |

| 4.9.2.2                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                         |

| 4.9.2.3                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                         |

| 4.9.2.4                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                         |

| 4.9.2.5                                                                                                                                                                                     | GTX Links                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                         |

| 4.9.3                                                                                                                                                                                       | Rear GPIO Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                         |

| 4.9.4                                                                                                                                                                                       | System Monitorina                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                         |

| 4.10.1                                                                                                                                                                                      | Automatic Temperature Monitoring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                         |

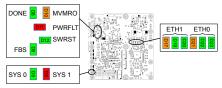

| 4.10.2                                                                                                                                                                                      | System Monitor Status LEDs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                         |

| 4.10.2                                                                                                                                                                                      | System Monitor Status LEDs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 20                                                                                                      |

| Annondiv                                                                                                                                                                                    | A Rear Connector Pinouts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 24                                                                                                      |

| A.1                                                                                                                                                                                         | Primary XMC Connector, P5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                         |

| A 2                                                                                                                                                                                         | Secondary XMC Connector, P5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                         |

| A.3                                                                                                                                                                                         | PMC Connector P4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                         |

| A.3                                                                                                                                                                                         | FINC COINECIOI F4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 23                                                                                                      |

| Annondiv                                                                                                                                                                                    | B Front (XRM) Connector Pinouts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24                                                                                                      |

| B.1                                                                                                                                                                                         | XRM Connector CN1, Field 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25                                                                                                      |

| B.2                                                                                                                                                                                         | XRM Connector CN1. Field 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                         |

| B.3                                                                                                                                                                                         | XRM Connector CN1, Field 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                         |

| B.4                                                                                                                                                                                         | XRM Connector CN2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                         |

|                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                         |

|                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                         |

| Annondiv                                                                                                                                                                                    | C YMC Breakout EPGA Pinout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 29                                                                                                      |

| Appendix                                                                                                                                                                                    | C XMC Breakout FPGA Pinout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 29                                                                                                      |